# The Network Management Unit (NMU): Securing Network Access For Direct-Connected FPGAs

Daniel Rozhko and Paul Chow

High-Performance Reconfigurable Computing Group · University of Toronto

February 26<sup>th</sup>, 2019

#### **FPGAs in Datacenters**

FPGAs are increasingly being deployed in datacenter and cloud environments

2

#### **FPGAs in Datacenters**

- FPGAs are increasingly being deployed in datacenter and cloud environments

- Major deployments are available by many vendors:

High-Performance Reconfigurable Computing Group · University of Toronto

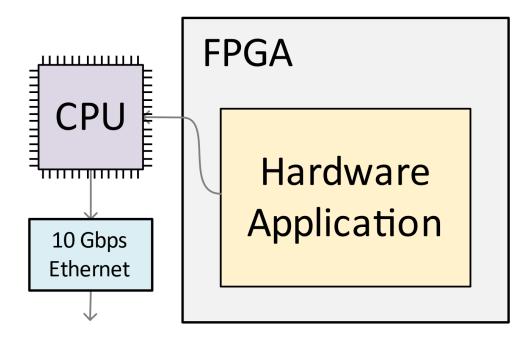

Traditional FPGA Connectivity Model – Accelerator

Traditional FPGA Connectivity Model – Accelerator

High-Performance Reconfigurable Computing Group · University of Toronto

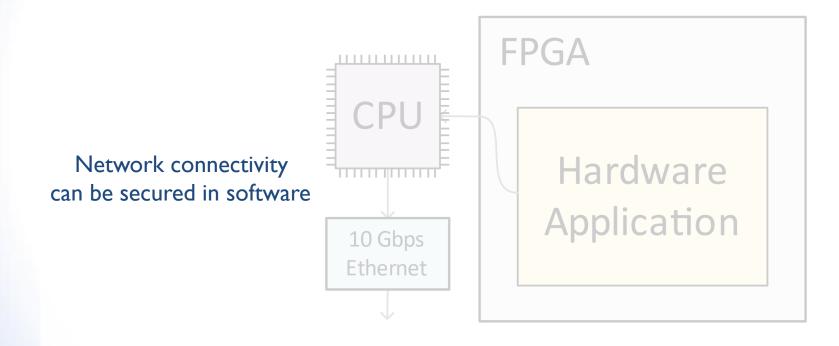

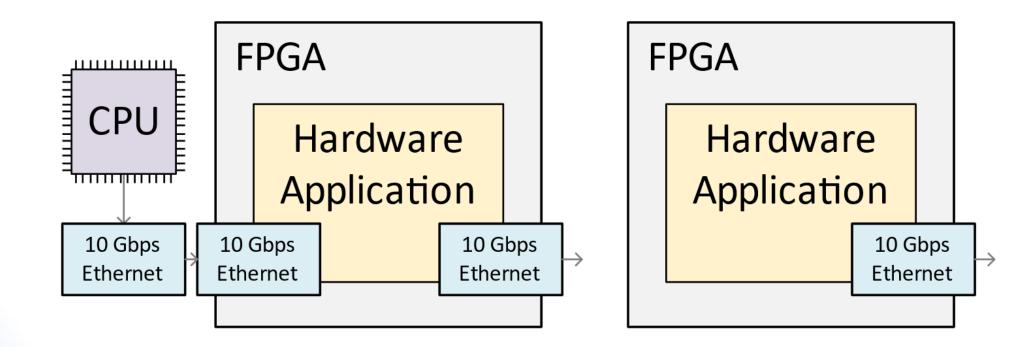

Increasingly Deployed Model – Direct-Connected FPGA

6

Increasingly Deployed Model – Direct-Connected FPGA

Network connectivity must be explicitly secured in hardware

High-Performance Reconfigurable Computing Group · University of Toronto

## **Securing Network Access for FPGAs**

• Why do we need to secure network connectivity?

8

# **Securing Network Access for FPGAs**

- Why do we need to secure network connectivity?

- Multi-user or multi-tenant environments

- Multiple applications can affect/observe network behaviour

- Un-trusted users (i.e. in cloud-like deployments)

- Network (potentially) exposed to errant or malicious behaviour

9

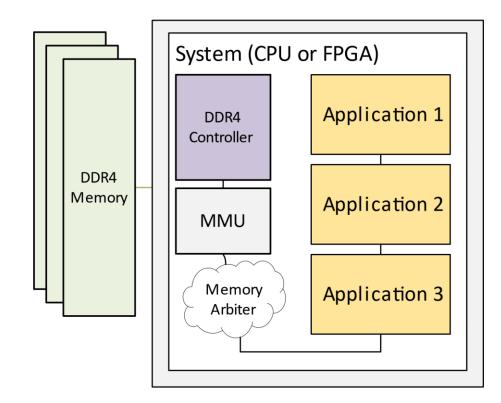

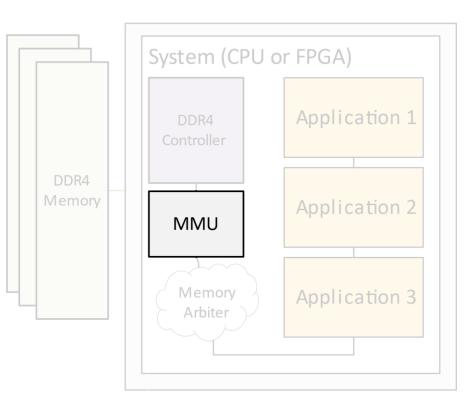

#### Analogue – Memory Management Unit (MMU)

An analogous shared resource – memory

# Analogue – Memory Management Unit (MMU)

An analogous shared resource – memory

MMU provides for each application:

- isolation to specific parts of memory

- rejection of invalid requests

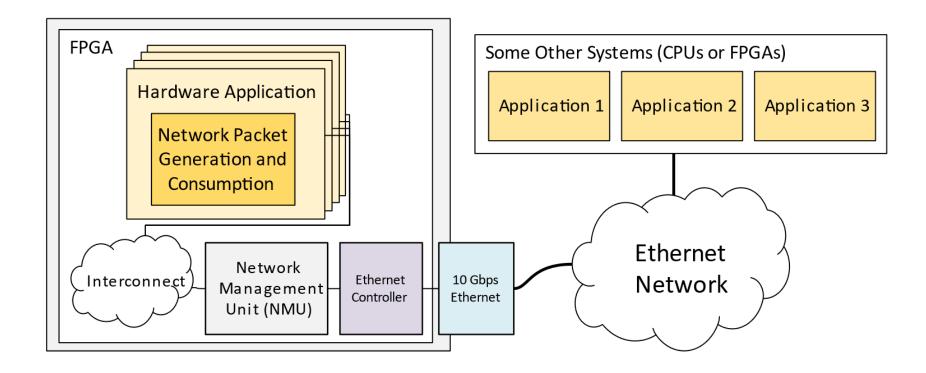

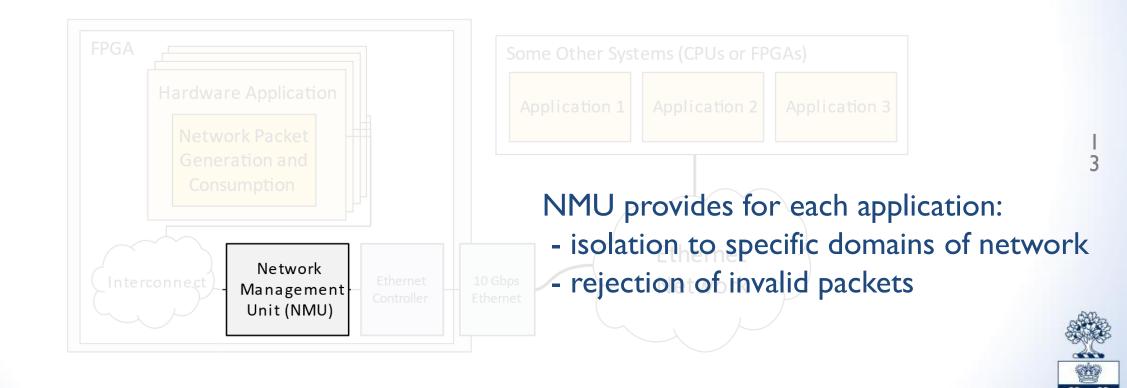

# **The Network Management Unit (NMU)**

Introducing the NMU

High-Performance Reconfigurable Computing Group · University of Toronto

# The Network Management Unit (NMU)

Introducing the NMU – securing network connectivity

# Outline

- Motivation for NMU

- NMU Architecture Types

- Our Hardware Implementation

- Evaluation of NMU Types

- Conclusions

# Outline

- Motivation for NMU

- NMU Architecture Types

- Our Hardware Implementation

- Evaluation of NMU Types

- Conclusions

High-Performance Reconfigurable Computing Group · University of Toronto

# **Previous Work – Hardware**

- Network security schemes from previous FPGA works

- Packet encapsulation

- MAC source address replacement

- Full network switch in soft-logic

- e.g. OpenFlow switch on FPGA

# **Previous Work – Hardware**

- Network security schemes from previous FPGA work

- Packet encapsulation (1)

- MAC source address replacement (2)

- Full network switch in soft-logic (3)

- e.g. OpenFlow switch on FPGA

• Either very simplistic (1,2) or high utilization (3)

## **Previous Work – Software**

- Firewalls

- Network Access Control Lists (NACL)

- Both Source and Destination Address ACLs

- Virtualization

- VLAN (tag-based), VXLAN, NVGRE (encapsulation-based)

- Hairpinning

- Pushing securitization to another switch or appliance

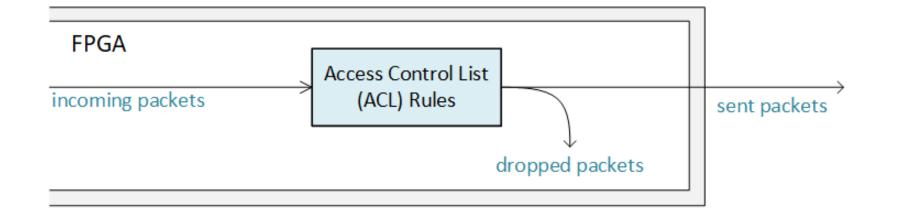

- Four main considerations identified for NMU design

- I) Access Controls Implemented

- 2) Support for Internal Routing

- 3) Virtual Networking Functionality

- 4) Network Layer of Operation

Q

- Four main considerations identified for NMU design

- I) Access Controls Implemented

ACLs can be implemented in the NMU, or in the downstream physical switch

- ACLs can be implemented in the NMU, or in the downstream physical switch

- Our classification of NMU Types:

Type A  $\rightarrow$  no ACLs implemented in NMU (802.1Qbg, 802.1pr)

- ACLs can be implemented in the NMU, or in the downstream physical switch

- Our classification of NMU Types:

Type A  $\rightarrow$  no ACLs implemented in NMU (802.1Qbg, 802.1pr)

Type  $B \rightarrow$  Sender Address ACLs only in NMU

- ACLs can be implemented in the NMU, or in the downstream physical switch

- Our classification of NMU Types:

Type A  $\rightarrow$  no ACLs implemented in NMU (802.1Qbg, 802.1pr)

Type  $B \rightarrow$  Sender Address ACLs only in NMU

Type C  $\rightarrow$  Sender and Destination Address ACLs in NMU

2

- ACLs can be implemented in the NMU, or in the downstream physical switch

- Our classification of NMU Types:

Type A  $\rightarrow$  no ACLs implemented in NMU (802.1Qbg, 802.1pr)

Type  $B \rightarrow$  Sender Address ACLs only in NMU

Type C  $\rightarrow$  Sender and Destination Address ACLs in NMU

Type  $E \rightarrow$  Encapsulation, no ACLs necessary

High-Performance Reconfigurable Computing Group · University of Toronto

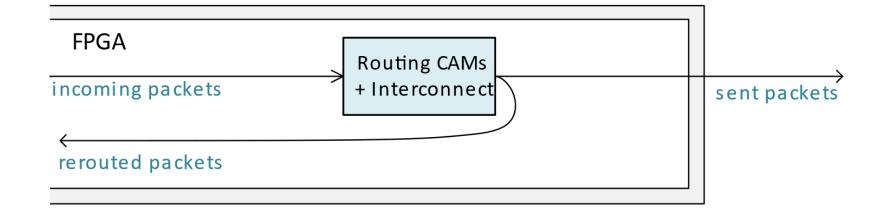

- Four main considerations identified for NMU design

- 2) Support for Internal Routing

- Four main considerations identified for NMU design

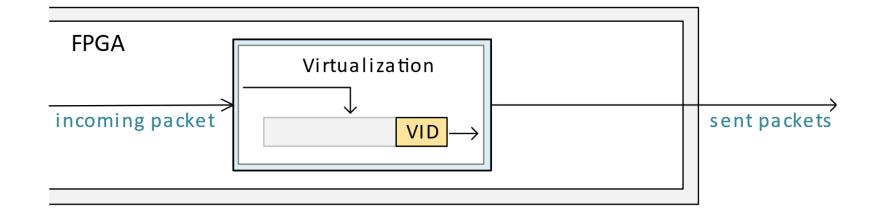

- 3) Virtual Networking Functionality

- Four main considerations identified for NMU design

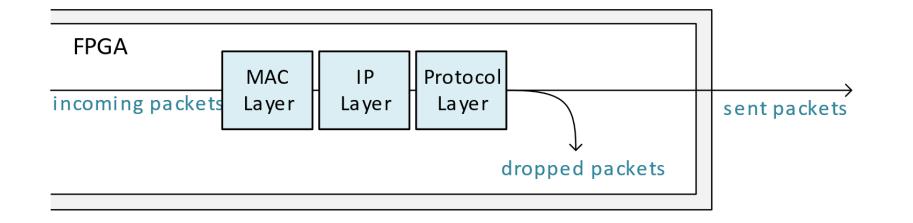

- 4) Network Layer of Operation

# Outline

- Motivation for NMU

- NMU Architecture Types

- Our Hardware Implementation

- Evaluation of NMU Types

- Conclusions

2

High-Performance Reconfigurable Computing Group · University of Toronto

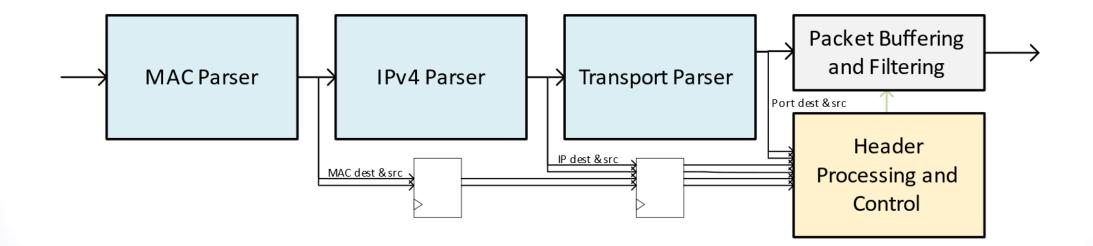

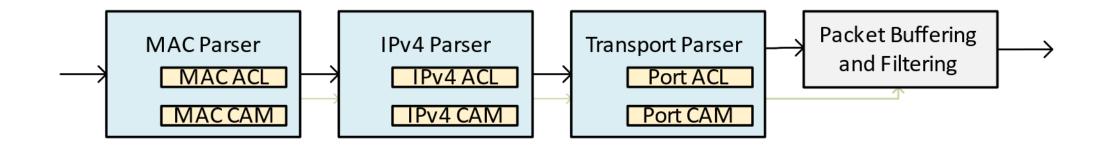

## **Principal Hardware Sub-Components**

- Three main reusable sub-components

- a) Packet Parsers

- b) Encapsulator/Tagger

- c) De-Encapsulator/De-Tagger

3

#### **Traditional Packet Parsers**

• Traditional packet parser system:

• Traditional packet parser, but with processing done in flight

3

• Traditional packet parser, but with processing done in flight

• Traditional packet parser, but with processing done in flight

• Traditional packet parser, but with processing done in flight

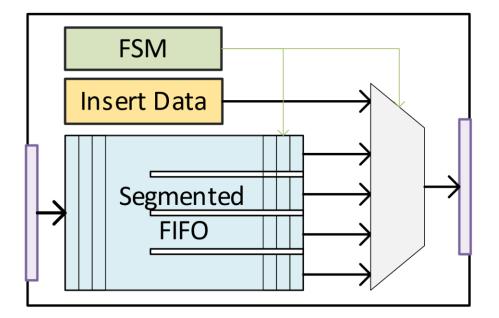

#### **Encapsulators/Taggers**

• Packet split into segment FIFOs, read out with inserted data

Ď

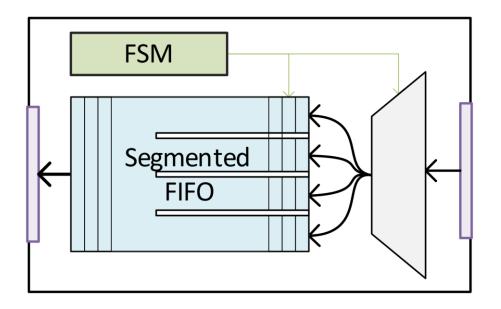

#### **De-Encapsulators/De-Taggers**

Data to be removed from packet never inserted into FIFOs

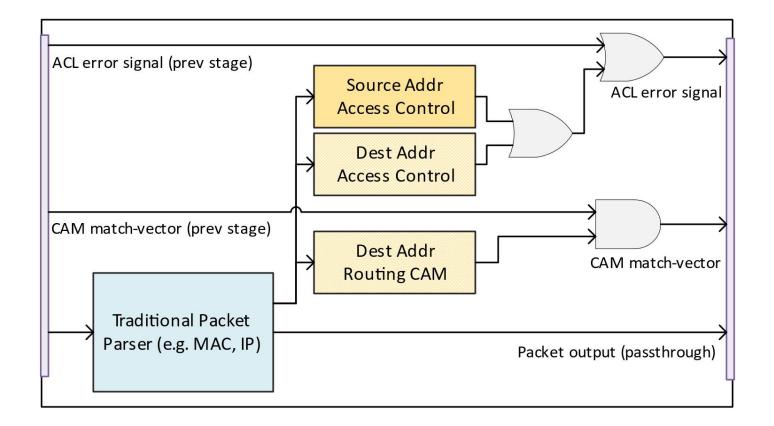

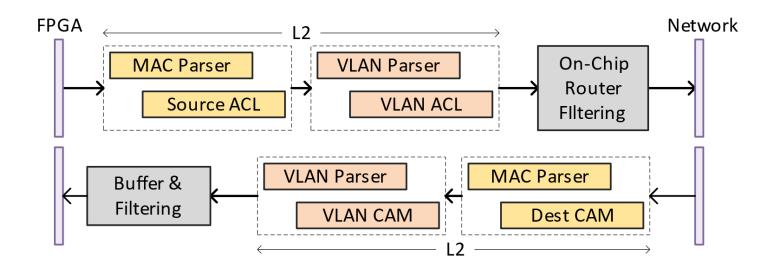

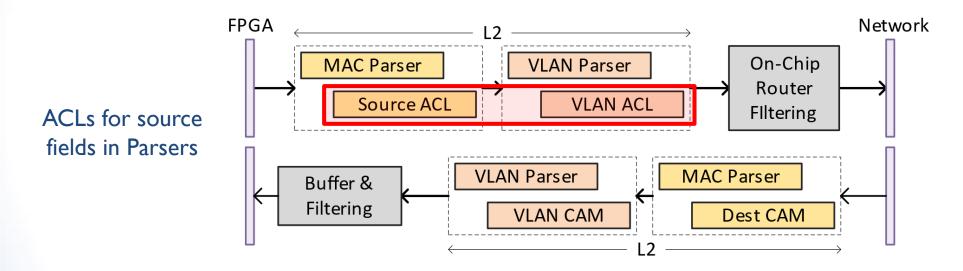

• Type B-L2 NMU (source ACLs, MAC layer processing)

• Type B-L2 NMU (source ACLs, MAC layer processing)

3

• Type B-L2 NMU (source ACLs, MAC layer processing)

• Type B-L2 NMU (source ACLs, MAC layer processing)

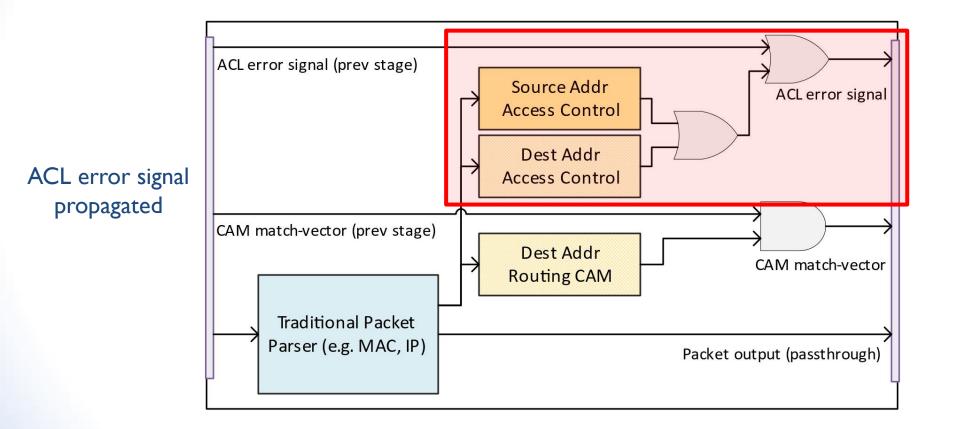

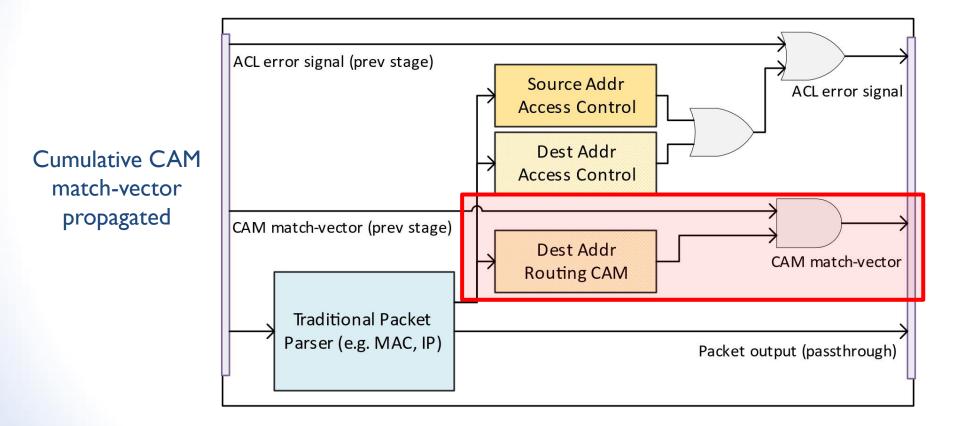

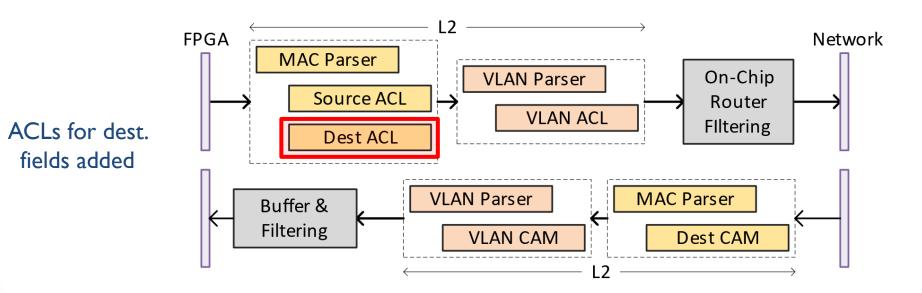

Type C-L2 NMU (source & dest ACLs)

2

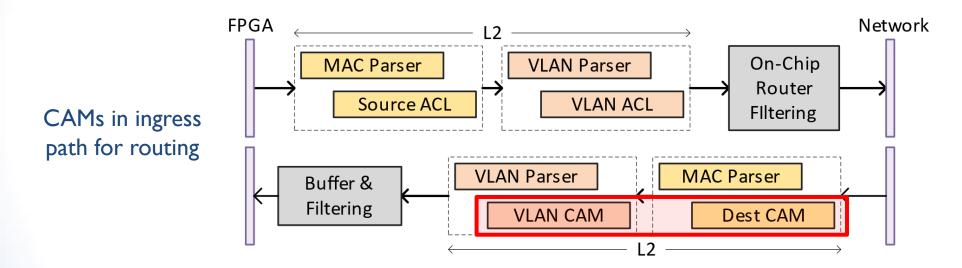

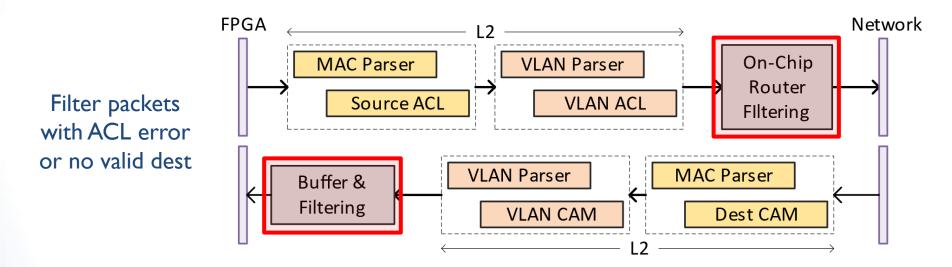

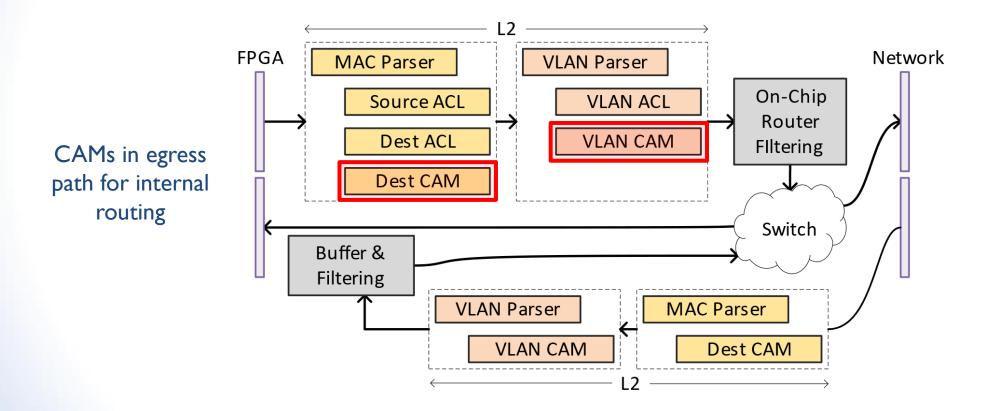

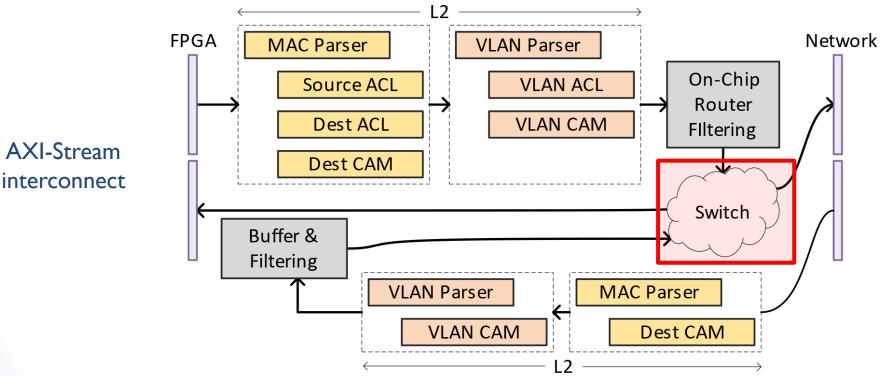

• Type CR-L2 NMU (adding internal routing)

Ť

Type CR-L2 NMU (adding internal routing)

interconnect

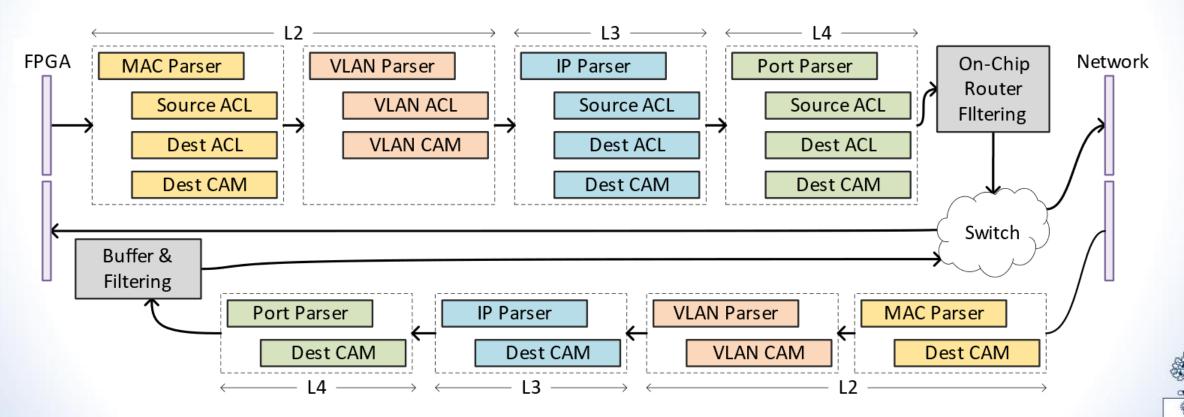

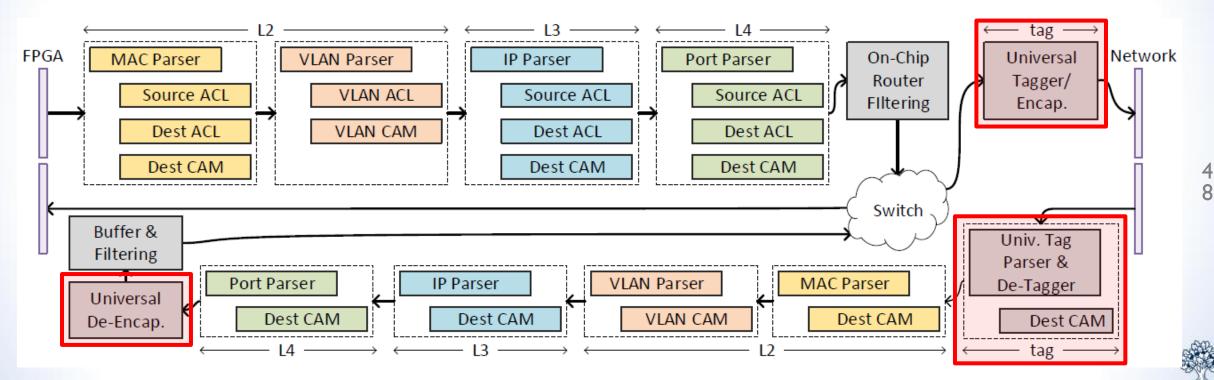

Type CR-L4 NMU (expanding to layer 4 packet processing)

High-Performance Reconfigurable Computing Group · University of Toronto

Ď

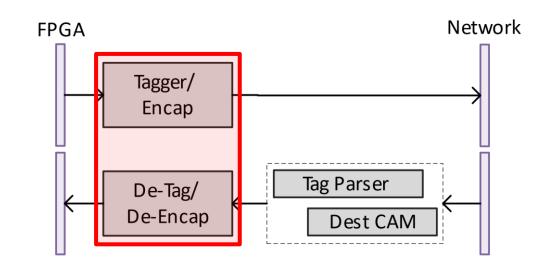

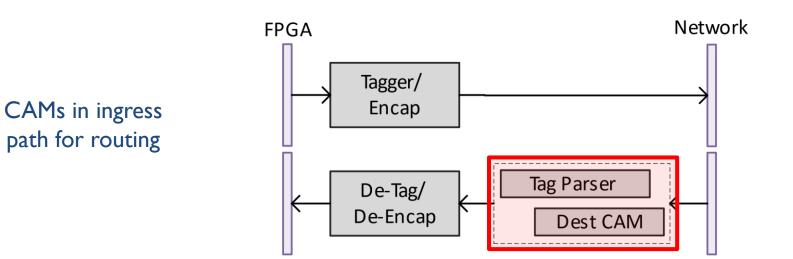

• Type A (tagging) and Type E (encapsulation)

tag/encap on egress de-tag/de-encap on ingress

• Type A (tagging) and Type E (encapsulation)

February 26<sup>th</sup>, 2019

ĕ

The Universal NMU

Add encap/de-encap components to L4 NMU architecture

#### **Multi-Tenant Considerations**

- Can have multiple applications on one FPGA

- NMU needs to secure multiple logical connections separately

- We implement NMUs with 32 logical connections

0

## Outline

- Motivation for NMU

- NMU Architecture Types

- Our Hardware Implementation

- Evaluation of NMU Types

- Conclusions

5

#### **Evaluation Setup**

• What qualities of NMUs characterize its performance?

### **Evaluation Setup**

- What qualities of NMUs characterize its performance?

- Throughput (I0Gbps line-rate, no need to measure)

- Area (need to measure LUT/FF utilization)

- Latency (need to measure cycles added in ingress/egress path)

freq. =156.25 MHz (freq. of Ethernet controller)

5

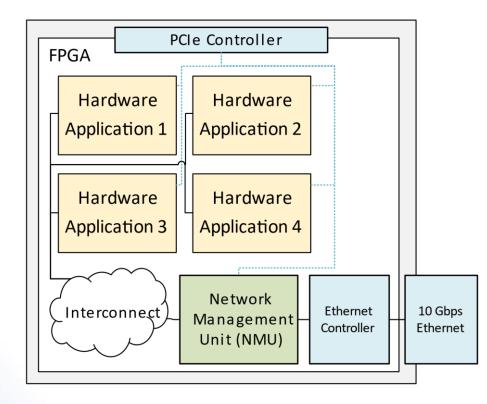

### **Evaluation Setup**

Four simple hardware applications on one FPGA

- Configured over PCIe

- 32 logical connections

- 4 applications x 8 connections

- Kintex Ultrascale XCKUI15

53

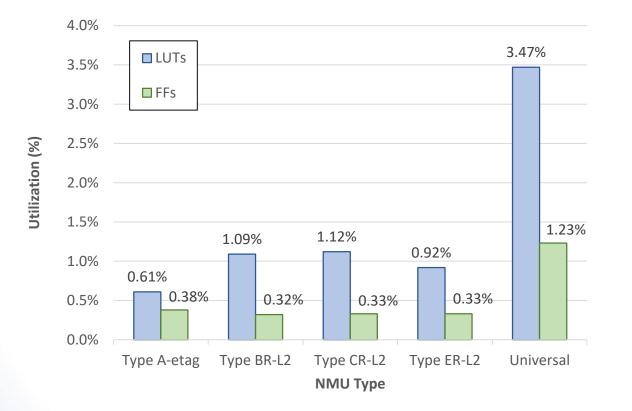

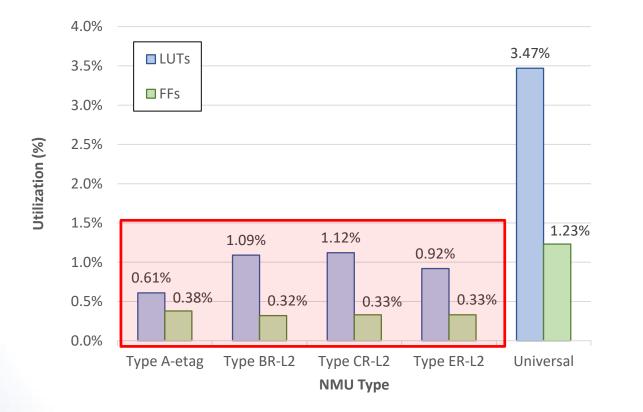

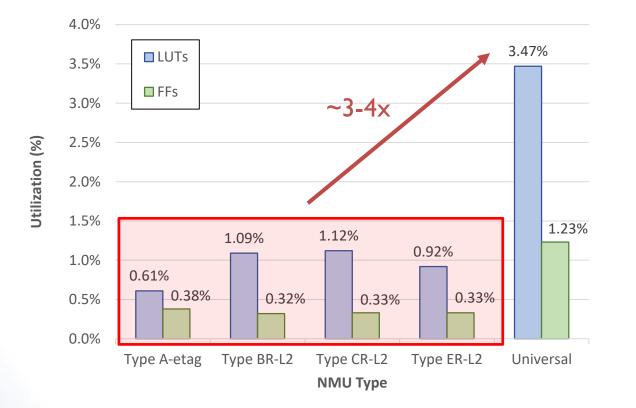

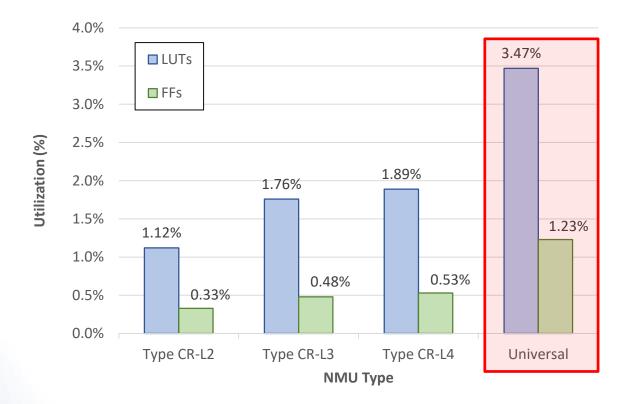

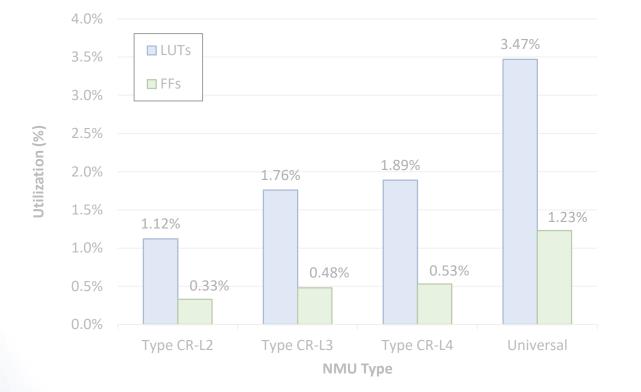

#### Area Comparison

#### Area Comparison

#### Not much difference in utilization between NMU Types

Ď

#### Area Comparison

Overhead of Universal NMU is about 3-4x (but still small) Ď

February 26<sup>th</sup>, 2019

#### Area Comparison

#### 4.0% 3.47% LUTs 3.5% FFs 3.0% 2.5% Utilization (%) 2.0% 1.5% 1.23% 1.12% 1.09% 0.92% 1.0% 0.61% 0.38% 0.33% 0.32% 0.5% 0.33% 0.0% Type CR-L2 Type ER-L2 Type A-etag Type BR-L2 Universal **NMU Type**

#### Latency (cycles)

|             | Egress | Ingress |

|-------------|--------|---------|

| Type A-etag | 1      | 4-6     |

| Type BR-L2  | 5-10   | 6-8     |

| Type CR-L2  | 5-10   | 6-8     |

| Type ER-L2  | 6-7    | 8-10    |

| Universal   | 13-18  | 19-25   |

Impact on latency of Universal NMU is more pronounced 5

Ď

#### **NMU Evaluation – Routability**

#### Area Comparison:

|           | Without Routing |      | With Routing |      | Overhead |       |

|-----------|-----------------|------|--------------|------|----------|-------|

|           | LUTs            | FFs  | LUTs         | FFs  | LUTs     | FFs   |

| Type B-L2 | 3516            | 2883 | 7199         | 4311 | 2.04x    | I.50x |

| Type C-L2 | 3687            | 2867 | 7424         | 4378 | 2.01×    | I.53x |

| Type E-L2 | 3392            | 3113 | 6133         | 4316 | 1.81x    | 1.39x |

#### **NMU Evaluation – Routability**

Latency Comparison (in cycles):

|           | Without Routing |         | With Routing |         | Overhead |          |

|-----------|-----------------|---------|--------------|---------|----------|----------|

|           | Egress          | Ingress | Egress       | Ingress | Egress   | Ingress  |

| Type B-L2 | I-6             | 2-4     | 5-10         | 6-8     | 4 cycles | 4 cycles |

| Type C-L2 | I-6             | 2-4     | 5-10         | 6-8     | 4 cycles | 4 cycles |

| Type E-L2 | I               | 4-6     | 6-7          | 8-10    | 5-6 сус. | 4 cycles |

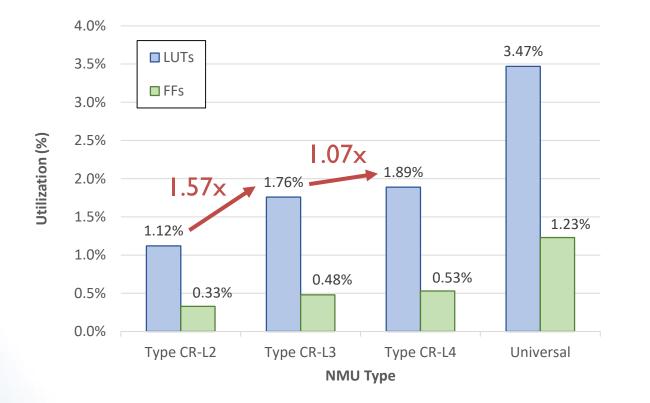

#### **NMU Evaluation – Network Layer**

#### Area Comparison

Overhead of IP Layer inspection significant, but not significant for Transport Layer

6

February 26th, 2019

#### **NMU Evaluation – Network Layer**

#### Area Comparison

Universal NMU overhead is still high, 1.8-2x Þ

6

#### **NMU Evaluation – Network Layer**

#### Area Comparison

#### Latency (cycles)

|            | Egress | Ingress |

|------------|--------|---------|

| Type CR-L2 | 5-10   | 6-8     |

| Type CR-L3 | 6-11   | 7-12    |

| Type CR-L4 | 6-11   | 7-12    |

Not much difference in latency

6

2

P

### **NMU Variety Evaluation Summary**

- Area

- Routability has biggest impact on area utilization

- Jumping from MAC to IP processing also has a big impact, though the jump from IP to Transport protocol is less severe

- All implementations have low area overhead

- Latency

- Routability has single biggest impact on latency as well

- Universal NMU has a big latency hit

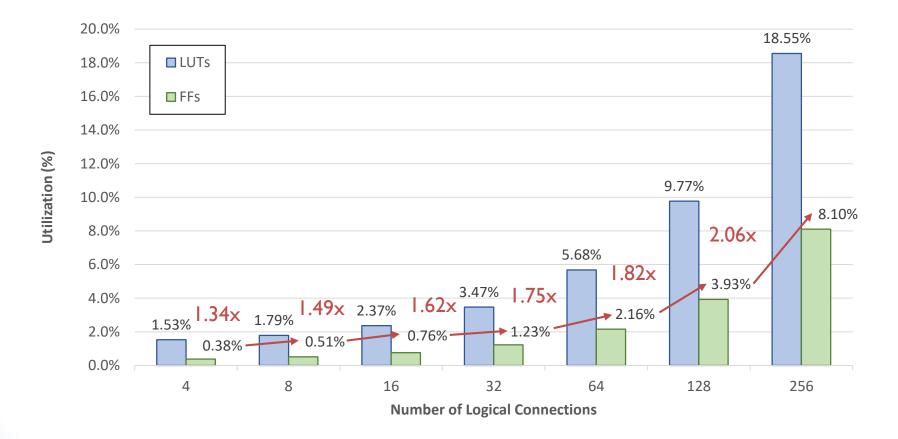

#### **Universal NMU Scalability**

Scaling Number of Logical Connections

#### **Universal NMU Scalability**

Scaling Number of Logical Connections

## Outline

- Motivation for NMU

- NMU Architecture Types

- Our Hardware Implementation

- Evaluation of NMU Types

- Conclusions

### Conclusions

- The NMU is a low overhead network security solution for direct-connected FPGAs, across many configurations

- Differences between NMU configurations are quite small, though Universal NMU does add significantly more latency

- Universal NMU can scale to 256 connections, with area hit

- Universal NMU effectively implements all NMU functionalities identified, may be candidate for hardening

#### **Acknowledgments**

We'd like to thank and acknowledge Xilinx, Hauwei, and NSERC for the funding, material, and support provided for this project

6

# **Questions?**

rozhkoda@eecg.toronto.edu

6

9

February 26<sup>th</sup>, 2019