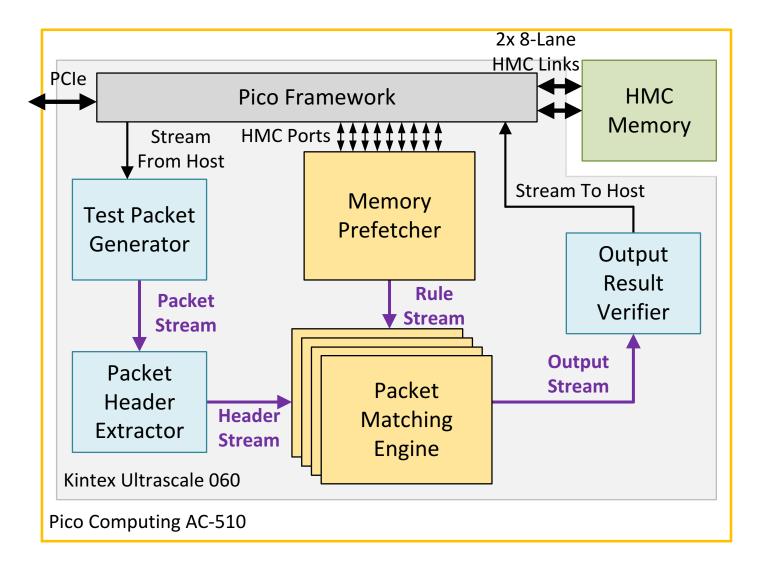

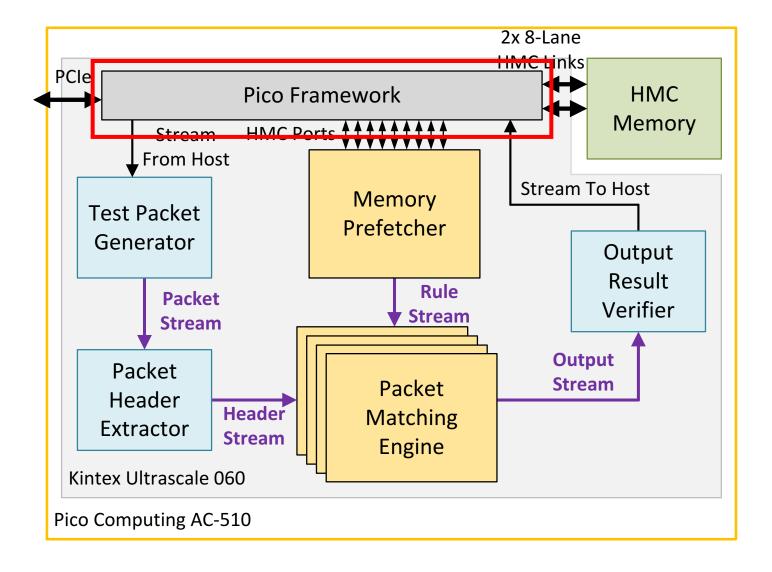

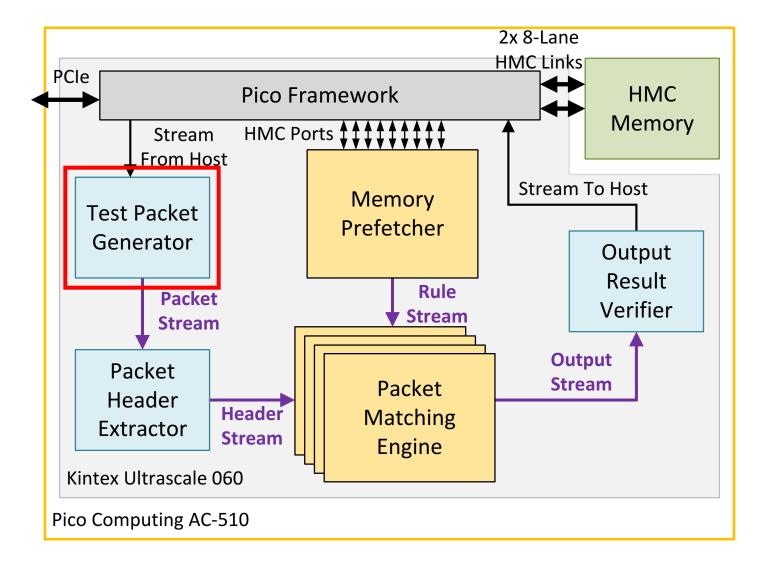

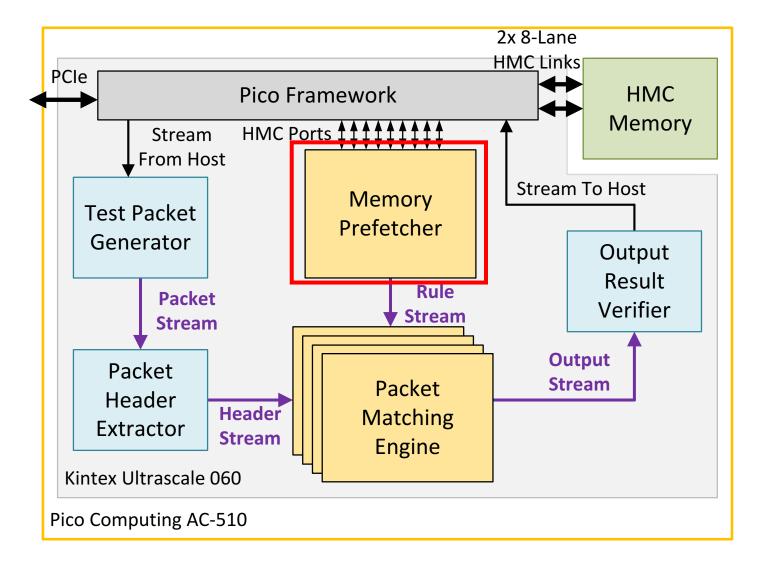

#### Packet Matching on FPGAs Using HMC Memory: Towards One Million Rules

Daniel Rozhko, Geoffrey Elliott, Daniel Ly-Ma, Paul Chow, Hans-Arno Jacobsen

Department of Electrical and Computer Engineering

University of Toronto

#### Motivation

- Packet processing is used to decide what to do with incoming packets to a network device

- Check packets against a list of rules (rulesets)

#### Motivation

- Packet processing is used to decide what to do with incoming packets to a network device

- Check packets against a list of rules (rulesets)

- Certain applications need very large rulesets

- On-chip FPGA implementations support a limited number of rules (<10K)</li>

- Traditional off-chip memory is too slow

#### Motivation

- Packet processing is used to decide what to do with incoming packets to a network device

- Check packets against a list of rules (rulesets)

- Certain applications need very large rulesets

- On-chip FPGA implementations support a limited number of rules (<10K)</li>

- Traditional off-chip memory is too slow

- Emerging high performance memories like Hybrid Memory Cube (HMC) could be a solution

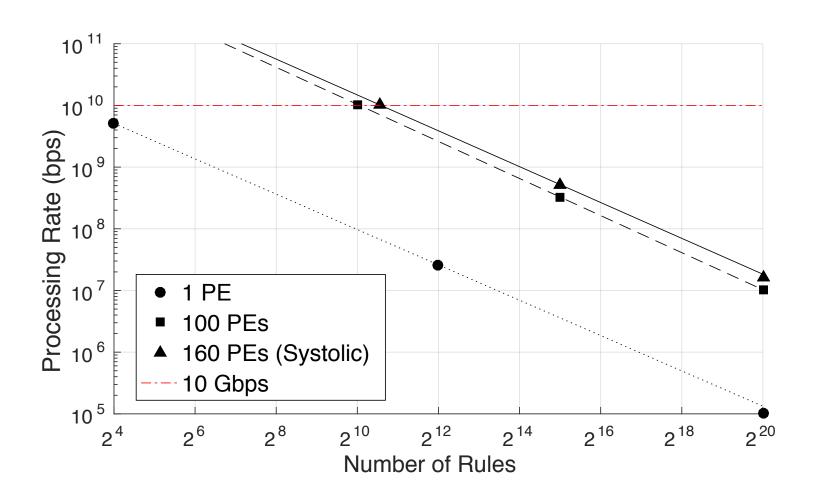

- 10G line rate at 1 million rules

## Experience with HLS

#### Experience with HLS

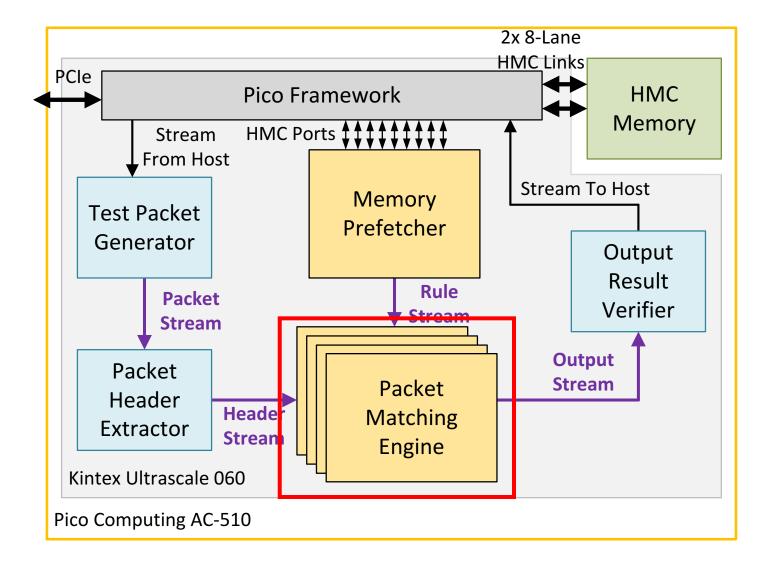

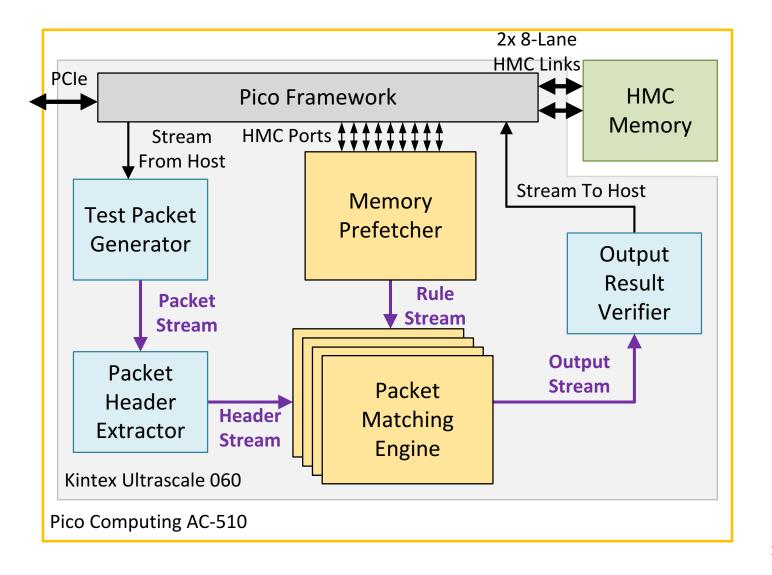

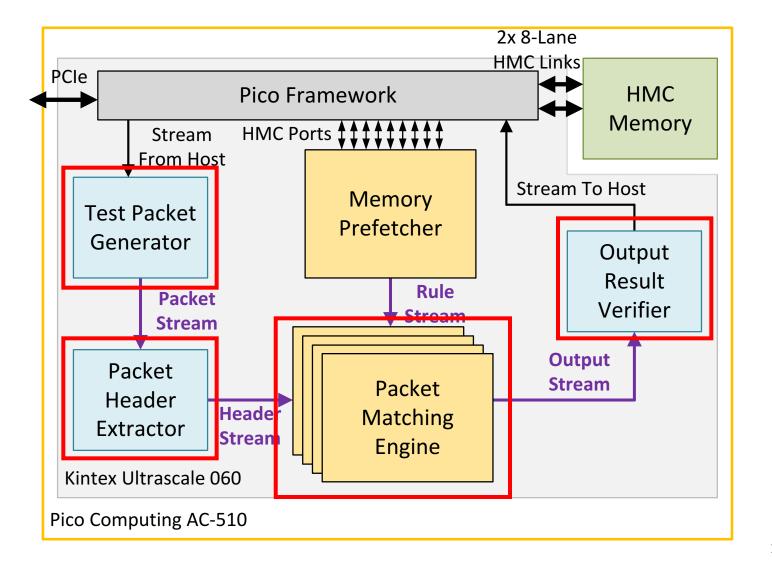

## Results - Throughput

# Please come visit our poster for more details!

Daniel Ly-Ma (d.lyma@mail.utoronto.ca)