# DESIGN SPACE EXPLORATION OF L1 DATA CACHES FOR FPGA-BASED MULTIPROCESSOR SYSTEMS

Eric Matthews, Nicholas Doyle and Lesley Shannon Simon Fraser University, Burnaby, BC, Canada

## MOTIVATION

Multicore systems are *everywhere*They have coherent shared memory, caches and operating system support

#### **OBJECTIVE**

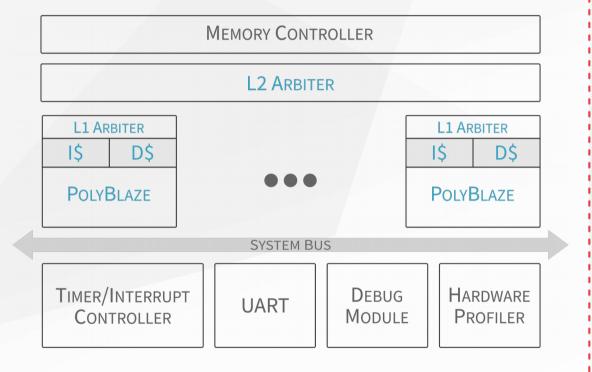

To extend the PolyBlaze framework with a fully coherent, highly configurable L1 cache implementation designed for FPGAs

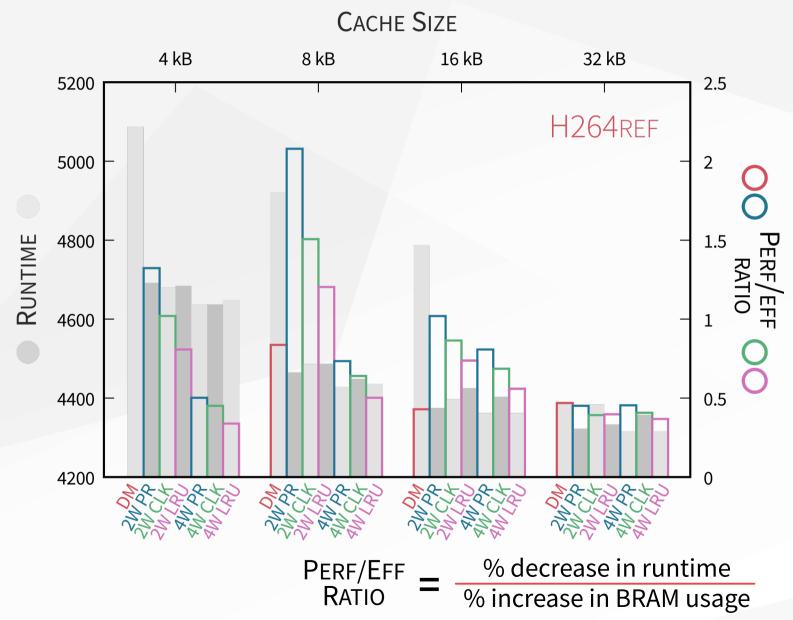

### Performance Efficiency Ratio

PERF/EFF = % decrease in runtime % increase in BRAM usage

Results relative to a 4KB Direct Mapped cache

## SYSTEM DESIGN

#### CACHE PROPERTIES

- Write Through

- Cache Size 4-32KB

- Coherency Support

- 1-4 Ways

- Replacement Polices

Direct Mapped (DM)

Pseudo Random (PR)

Clock (CLK)

Least Recently Used (LRU)

# RESULTS & CONCLUSIONS

## PSEUDO RANDOM

provides the highest Performance Effeciency Ratio

Results relative to a 4KB Direct Mapped cache